## **TEL AVIV UNIVERSITY**

## THE IBY AND ALADAR FLEISCHMAN FACULTY OF ENGINEERING Department of Electrical Engineering - Systems

Subject

# DESIGN AND IMPLEMENTATION OF PCI BUS BASED SYSTEMS

Thesis submitted toward the degree of

Master of Science in Electrical and Electronic Engineering

In Tel Aviv University

by

**Ehud Finkelstein**

October 1997

## **TEL AVIV UNIVERSITY**

## THE IBY AND ALADAR FLEISCHMAN FACULTY OF ENGINEERING Department of Electrical Engineering - Systems

Subject

# DESIGN AND IMPLEMENTATION OF PCI BUS BASED SYSTEMS

Thesis submitted toward the degree of

Master of Science in Electrical and Electronic Engineering

In Tel Aviv University

by

## **Ehud Finkelstein**

This research work was carried out at Tel-Aviv University in the Department of Electrical and Electronic Engineering,

Faculty of Engineering

under the supervision of Dr. Shlomo Weiss

October 1997

## **Acknowledgments**

I would like to thank a few people who helped me during this work:

Dr. Shlomo Weiss, for his helpful feedback, and his excellent examples of clear writing style.

My family, for their encouragement and support.

Dov Freund, for answering all my C++ questions when I needed it the most.

And finally, I would like to thank Stephen Craimer and FourFold technologies Ltd., for kindly letting me use all the PCI related research I have done (and still do) while working there.

#### **Abstract**

PCI is perhaps the most successful bus design ever made, both on the technical and the marketing levels. Our work is divided into several sections: reviewing computer busses in general, related bus protocols, bus design principles, reviewing the PCI protocol, discussing PCI implementations using programmable logic chips, and finally, we propose PCI protocol improvements, simulate them, and analyze the results.

In the first section present an introduction to computer busses and their various parameters. We also briefly review the following busses: ISA, LPC, MicroChannel, EISA, VESA Local Bus, VME, NuBUS, FutureBus+.

In the second section, we also review the following bus standards, derived from the basic PCI spec: PMC, CompactPCI, PXI, PCI-ISA, PISA, CardBus, AGP, HiRelPCI, PC/104-Plus, and SmallPCI.

In the third section we present background material including: synchronous logic design principles, synchronous vs. asynchronous bus overview, and backplane physics.

The next section contains a description of the PCI protocol, explaining the basic protocol operations and commands, configuration registers, and PCI to PCI bridges.

Section 5 contains background material on FPGA and CPLD chips, as well as design considerations for PCI masters and targets that are specific to CPLD and FPGA implementations (as opposed to ASIC implementations). Most of these design considerations are design tips, used to reduce the design size, and to achieve the 33MHz speed requirement. We also show a typical design flow used for designing and simulating PCI devices. Both the design flow and the CPLD implementation notes are based on an actual working implementation of a PCI card designed, built, and debugged by the author.

In the last section, we discuss one of the drawbacks of PCI, which is efficient handling of targets with a long initial read latency. We suggest three alternatives for solving this problem.

One alternative is to return a "retry hint" during the target retry cycle, indicating how long it would take the target to complete the transaction. Now the master can retry the cycle only when the data is available. Between these events, other bus masters may use the bus.

The other solution we propose is a new PCI command which posts multiple short read requests to the target. The data is returned by the target as one or more bus master write transactions. This has the effect of adding split bus transactions to PCI.

We present a complete simulation environment, including synchronous logic simulation, PCI protocol simulation, and simulation of our PCI extensions. We use the simulation environment to simulate the latency hint protocol extension using a test bench modeled as close as possible to a typical PCI bus configuration as found on common PCs.

The results we have shown are that on a typical PC load the "retry hint" protocol extension gains up to 4% improvement on the bus utilization.

## **Table of Contents**

| 1. INTRODUCTION TO THE PCI BUS ARCHITECTURE                     | 10 |

|-----------------------------------------------------------------|----|

| 2. COMPUTER BUSSES                                              | 11 |

| 2.1 HISTORICAL PERSPECTIVE                                      | 11 |

| 2.2 Bus Architectures                                           | 14 |

| 2.3 COMPARISON AND DESIGN TRADEOFFS                             | 21 |

| 3. PCI BUS RELATED STANDARDS                                    | 26 |

| 3.1 INDUSTRIAL APPLICATIONS: BACKPLANE EXPANSION                | 26 |

| 3.1.1 PCI-ISA Passive Backplane                                 | 27 |

| 3.1.2 PISA Passive Backplane                                    | 27 |

| 3.1.3 PMC - PCI Mezzanine Card                                  | 27 |

| 3.1.4 CompactPCI                                                |    |

| 3.1.5 PXI - PCI eXtensions for Instrumentation                  |    |

| 3.1.6 HiRelPCI - High Reliability PCI                           |    |

| 3.2 EMBEDDED SYSTEMS: SINGLE-BOARD COMPUTER EXPANSION           |    |

| 3.2.1 PC/104-Plus                                               |    |

| 3.3 LAPTOPS AND MOBILE SYSTEMS.                                 |    |

| 3.3.1 CardBus                                                   |    |

| 3.3.2 Small PCI                                                 |    |

| 3.4 3D Graphics: AGP                                            | 32 |

| 4. BUS DESIGN PRINCIPLES                                        | 35 |

| 4.1 THE PHYSICS OF THE BACKPLANE BUS                            | 35 |

| 4.2 SYNCHRONOUS VS. ASYNCHRONOUS BUSSES                         | 36 |

| 4.2.1 The relative merits of Synchronous and Asynchronous Buses | 37 |

| 4.2.2 Estimating timing requirements of a synchronous bus       |    |

| 4.2.3 Estimating timing requirements of an asynchronous bus     |    |

| 4.2.4 Improved asynchronous bus protocols                       |    |

| 4.2.5 Metastability Considerations for Asynchronous buses       |    |

| 4.2.6 Selecting a bus type                                      |    |

| 4.3 SYNCHRONOUS DESIGN METHODOLOGIES                            |    |

| 4.3.1 The general synchronous models                            |    |

| 4.3.2 Synchronous Logic design                                  |    |

| 4.3.3 Optimizing Synchronous Logic circuits                     |    |

| 4.3.4 Synchronous systems with multi-phase clocks               | 45 |

| 5. THE PCI BUS OPERATION                                        | 47 |

| 5.1 THE PCI BUS SIGNAL DESCRIPTION.                             |    |

| 5.1.1 Signal types                                              |    |

| 5.1.2 System Signals                                            |    |

| 5.1.3 Address/Data and Command                                  |    |

| 5.1.4 Interface Control                                         |    |

| 5.1.5 Arbitration                                               |    |

| 5.1.6 Error Reporting                                           |    |

| 5.1.7 64 Bit Extension                                          |    |

| 5.1.8 Bus Snooping                                              |    |

| 5.1.9 JTAG (IEEE 1149.1)                                        |    |

| 5.2 THE PCI BUS COMMANDS.                                       |    |

| 5.3 THE PCI ADDRESS STRUCTURE                                   |    |

| 5.3.1 Memory address space                                      |    |

| 5.3.2 I/O address space                                         |    |

| 5.3.3 Configuration address space                               | 54 |

| 5.4 THE PCI CONFIGURATION HEADER                  |     |

|---------------------------------------------------|-----|

| 5.5 BASIC PCI CYCLES                              |     |

| 5.5.1 PCI Memory or I/O Read Cycle                |     |

| 5.5.2 PCI Memory or I/O Write Cycle               |     |

| 5.5.3 PCI Configuration Read Cycle                |     |

| 5.5.4 PCI Configuration Write Cycle               |     |

| 5.6 ABNORMAL CYCLE TERMINATION                    |     |

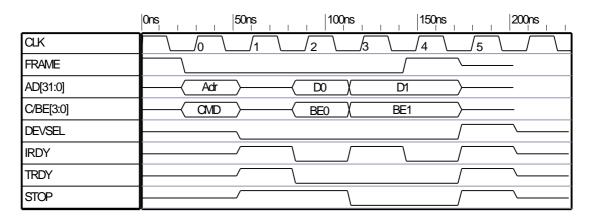

| 5.6.1 Target termination (Disconnect with data)   |     |

| 5.6.2 Disconnect without data                     |     |

| 5.6.3 Target Retry (Disconnect without data)      |     |

| 5.6.4 Target abort                                |     |

| 5.6.5 Master abort                                |     |

| 5.7 THE PCI TO PCI BRIDGE                         | 63  |

| 6. IMPLEMENTATION OF PCI DEVICES                  | 67  |

| 6.1 PCI IMPLEMENTATION USING CPLDS AND FPGAS      | 67  |

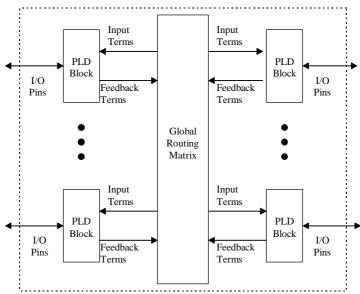

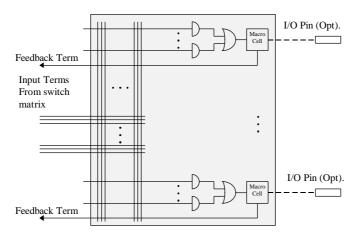

| 6.1.1 General structure of a CPLD                 | 68  |

| 6.1.2 General structure of an FPGA                | 69  |

| 6.1.3 Comparing FPGAs with CPLDs                  |     |

| 6.1.4 PCI Bus considerations                      |     |

| 6.2 THE HDL DESIGN FLOW                           | 78  |

| 6.2.1 A DSL to Verilog model translator           |     |

| 6.3 A PCI Bus simulation environment (test bench) | 80  |

| 6.3.1 A PCI Verilog test bench                    |     |

| 6.3.2 Synthesizable vs. Non-Synthesizable models  |     |

| 6.4 REAL WORLD TEST VECTOR INTEGRATION            |     |

| 6.5 HARDWARE-SOFTWARE CO-SIMULATION               |     |

| 6.6 AN ACTUAL PCI TARGET IMPLEMENTATION           | 83  |

| 7. IMPROVING THE PCI BUS                          | 85  |

| 7.1 THE LATENCY PROBLEM                           | 85  |

| 7.2 THE LATENCY HINT SOLUTION                     | 85  |

| 7.3 THE EARLY READ SOLUTION                       | 86  |

| 7.4 THE SPLIT TRANSACTION SOLUTION                | 86  |

| 7.4.1 The AGP protocol extensions                 |     |

| 7.5 PERFORMANCE ANALYSIS                          |     |

| 7.5.1 Collecting PCI traffic information          | 89  |

| 7.5.2 Generating PCI bus traffic simulation       |     |

| 7.5.3 Implementing the simulation framework       |     |

| 7.5.4 The simulation library classes              |     |

| 7.5.5 The simulation environment                  |     |

| 7.5.6 Simulation results and conclusions          | 99  |

| 8. BIBLIOGRAPHY                                   |     |

| APPENDIX A - ISA PROTOCOL SUMMARY                 | 109 |

| APPENDIX B - NUBUS PROTOCOL SUMMARY               | 117 |

| APPENDIX C - PCI CLASS CODES                      | 122 |

| APPENDIX D - GLOSSARY                             | 124 |

## **Table of Figures**

| FIGURE 1 - CLASSIC ISA SYSTEM                                                                   |    |

|-------------------------------------------------------------------------------------------------|----|

| FIGURE 2 - MODERN ISA SYSTEM.                                                                   |    |

| FIGURE 3 - MICROCHANNEL ARCHITECTURE                                                            |    |

| Figure 4 - FutureBus+ architecture                                                              |    |

| Figure 5 - PCI architecture                                                                     |    |

| FIGURE 6 - PMC MODULES MOUNTED ON A VME64 BOARD                                                 | 28 |

| FIGURE 7 - 3U AND 6U FORM FACTOR EUROCARDS                                                      |    |

| FIGURE 8 - PC/104 AND PC/104-PLUS CARDS                                                         |    |

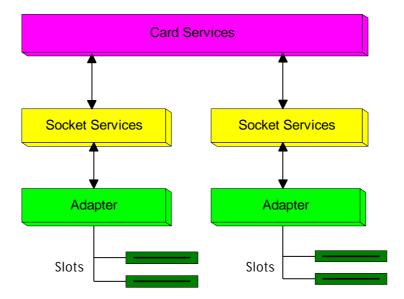

| FIGURE 9 - PC CARD AND CARDBUS SOFTWARE SUPPORT                                                 | 32 |

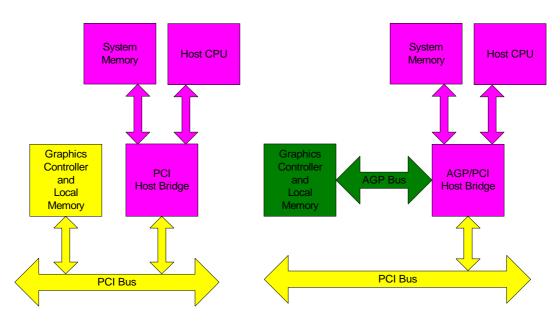

| FIGURE 10 - SYSTEM ARCHITECTURE: AGP/PCI vs. PCI only                                           | 33 |

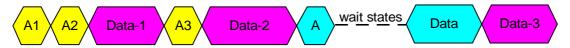

| FIGURE 11 - AGP BUS TRANSACTION PIPELINING AND INTERLEAVING                                     | 34 |

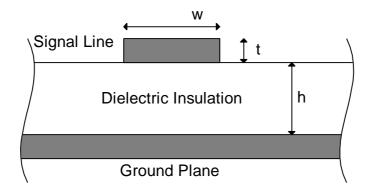

| FIGURE 12 - CROSS SECTION OF A MICROSTRIP BUS LINE                                              | 35 |

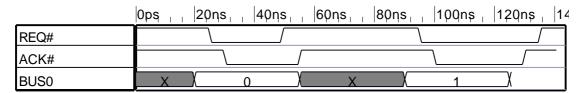

| FIGURE 13 - 4 PHASE ASYNCHRONOUS DATA TRANSFER                                                  | 37 |

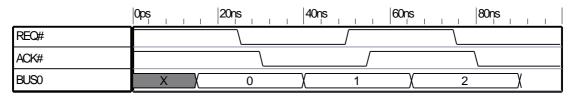

| FIGURE 14 - SYNCHRONOUS DATA TRANSFER                                                           | 37 |

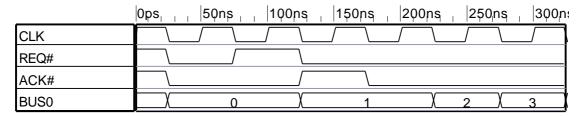

| FIGURE 15 - SYNCHRONOUS LOGIC TIMING MODEL                                                      |    |

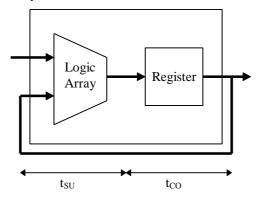

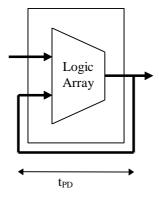

| FIGURE 16 - ASYNCHRONOUS LOGIC TIMING MODEL                                                     |    |

| FIGURE 17 - 2 PHASE ASYNCHRONOUS DATA TRANSFER                                                  |    |

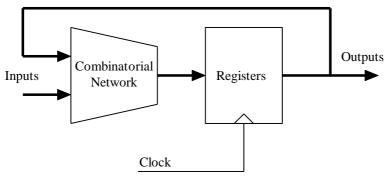

| FIGURE 18 - THE GENERAL SYNCHRONOUS MODEL                                                       |    |

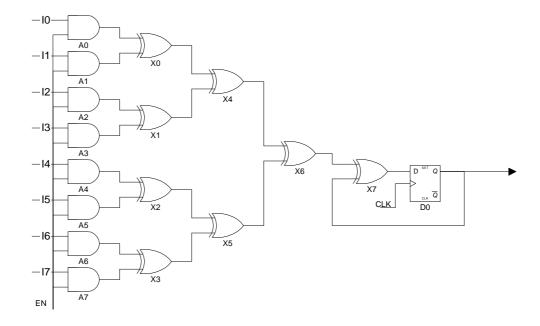

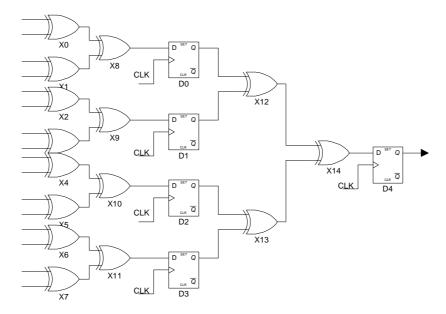

| FIGURE 19 - PARITY GENERATOR EXAMPLE                                                            |    |

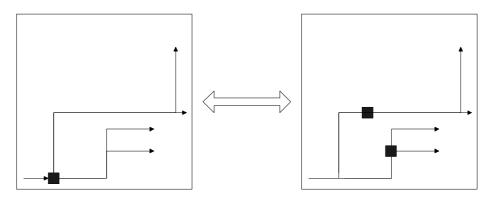

| FIGURE 20 - RETIMING TRANSFORMATION.                                                            |    |

| FIGURE 21 - PARITY GENERATOR EXAMPLE - RETIMING EXAMPLE NO. 1                                   |    |

| FIGURE 22 - PARITY GENERATOR EXAMPLE - RETIMING EXAMPLE NO. 2.                                  |    |

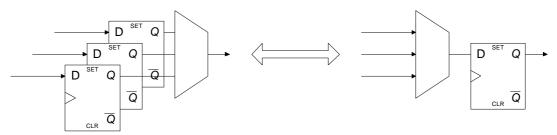

| FIGURE 23 - FANOUT CONTROL BY REPLICATING REGISTERS                                             |    |

| FIGURE 24 - THE EFFECT OF REGISTER REPLICATION ON FPGA/ASIC PATH LENGTH                         |    |

| FIGURE 25- LATENCY VS. THROUGHPUT.                                                              |    |

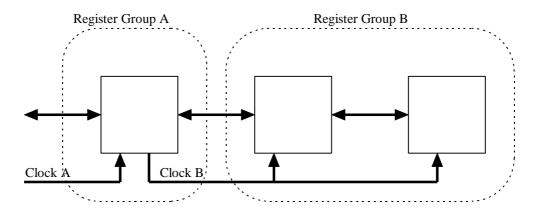

| FIGURE 26 - GROUPING DIFFERENT SYNCHRONOUS CLOCK ZONES.                                         |    |

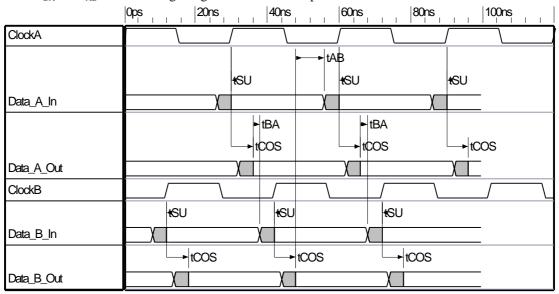

| FIGURE 27 - TIMING ANALYSIS FOR MULTI PHASE SYNCHRONOUS SYSTEMS                                 |    |

| FIGURE 28 - PCI CONFIGURATION HEADER 0                                                          |    |

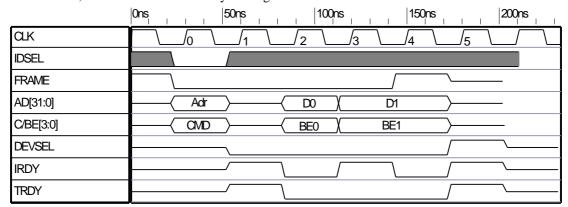

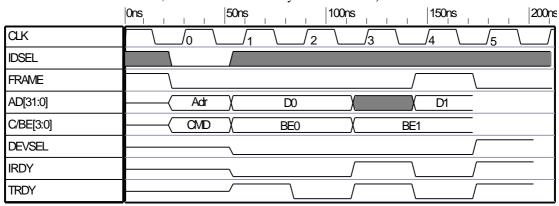

| FIGURE 29 - PCI MEMORY AND I/O READ CYCLE.                                                      |    |

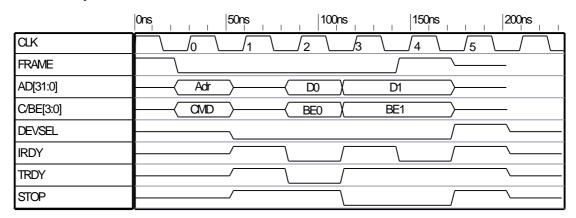

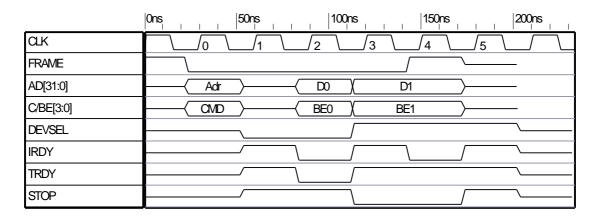

| FIGURE 30 - PCI MEMORY AND I/O WRITE CYCLE                                                      |    |

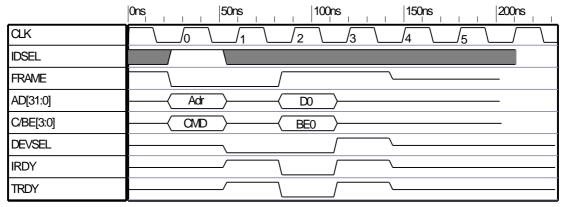

| FIGURE 31 - PCI CONFIGURATION READ CYCLE                                                        |    |

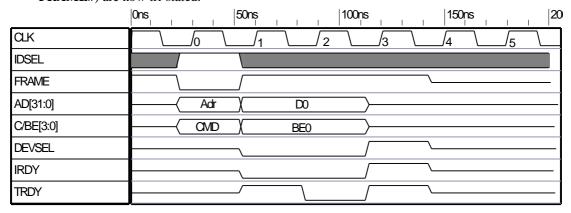

| FIGURE 32 - PCI CONFIGURATION WRITE CYCLE                                                       |    |

| FIGURE 33 - TARGET DISCONNECT WITH DATA                                                         |    |

| FIGURE 33 - TARGET DISCONNECT WITH DATA                                                         |    |

| FIGURE 35 - TARGET ABORT                                                                        |    |

|                                                                                                 |    |

| FIGURE 36 - PCI CONFIGURATION HEADER 1                                                          |    |

| FIGURE 37 - A GENERAL CPLD MODEL.                                                               |    |

| FIGURE 38 - PLD BLOCK STRUCTURE                                                                 | 69 |

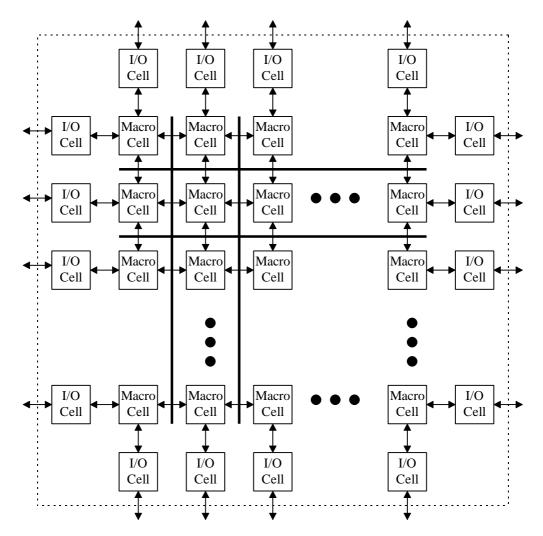

| FIGURE 39 - A GENERAL FPGA MODEL                                                                |    |

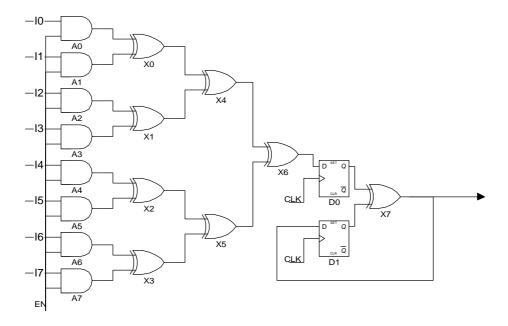

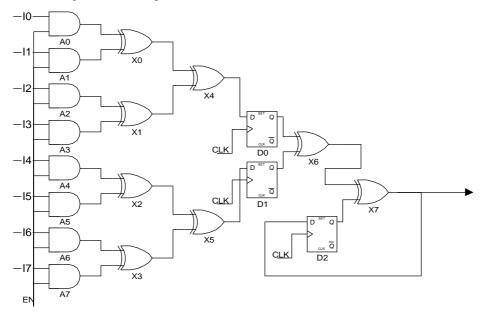

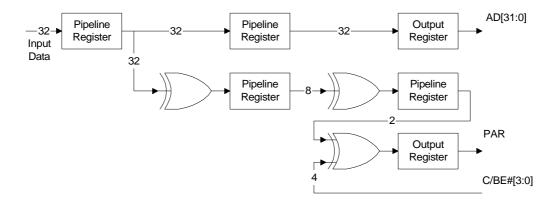

| FIGURE 40 - PIPELINED READ PARITY IMPLEMENTATION                                                |    |

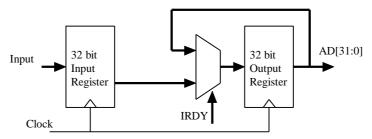

| FIGURE 41 - IRDY SIGNAL PATH IN PCI TARGET DESIGNS                                              |    |

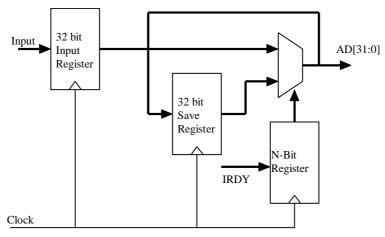

| FIGURE 42 - ALTERNATE IRDY SIGNAL PATH DESIGN                                                   |    |

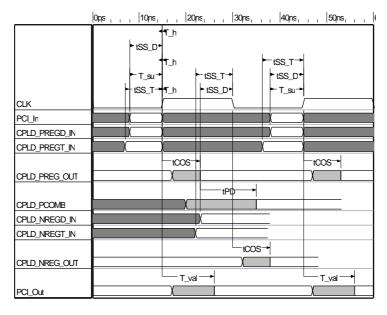

| FIGURE 43 - PCI COMPLIANT STATIC TIMING ANALYSIS FOR MACH 465-12                                |    |

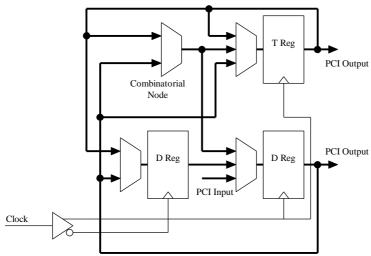

| FIGURE 44 - PCI COMPLIANT DATA FLOW IN A MACH 465 CPLD.                                         | 74 |

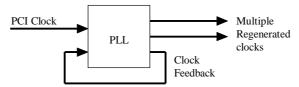

| FIGURE 45 - A PLL BASED CLOCK REGENERATOR CIRCUIT                                               | 75 |

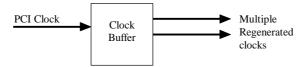

| FIGURE 46 - USING A CLOCK BUFFER                                                                |    |

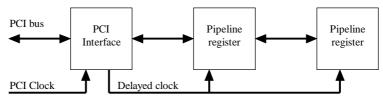

| FIGURE 47 - A SYNCHRONOUS MULTI PHASE BASED PCI SYSTEM                                          | 76 |

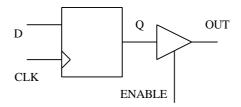

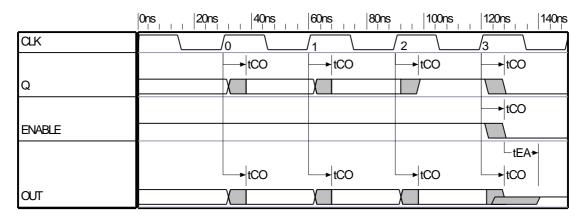

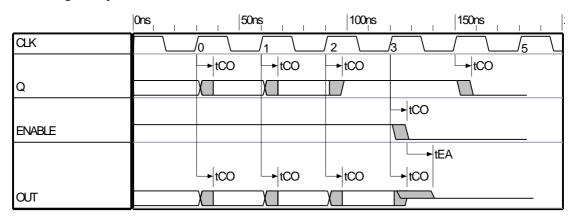

| FIGURE 48 - TYPICAL REGISTER OUTPUT STAGE                                                       |    |

| Figure 49 - Potential s/t/s spikes caused by simultaneous ENABLE and $\boldsymbol{Q}$ switching |    |

| Figure 50 - Solving s/t/s spikes by keeping $\boldsymbol{Q}$ high for one extra cycle           | 78 |

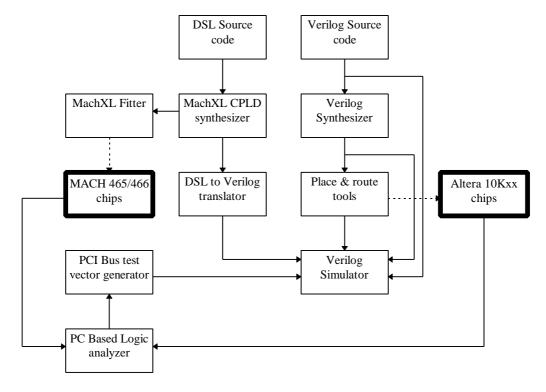

| FIGURE 51 - TYPICAL HDL DESIGN FLOW.                                                            | 79 |

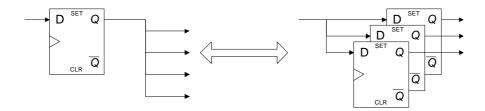

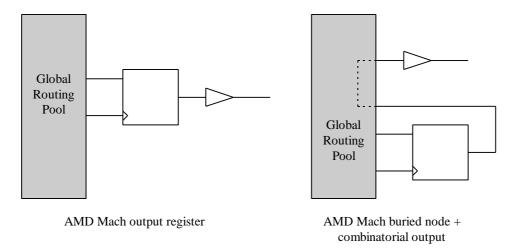

| Figure 52 - Alternative methods for implementing registered outputs on AMD MACH                 |    |

| DEVICES                                                                                         | 80 |

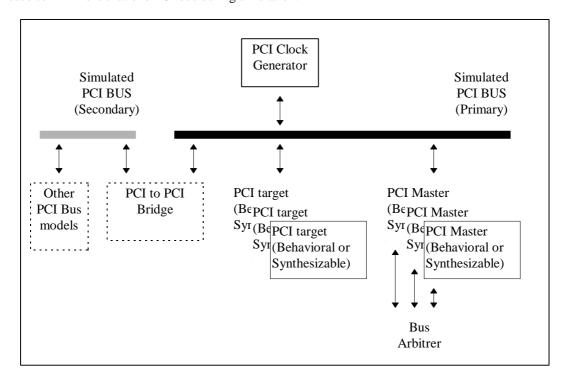

| FIGURE 53 - A TYPICAL PCI TEST BENCH                                                            | 81 |

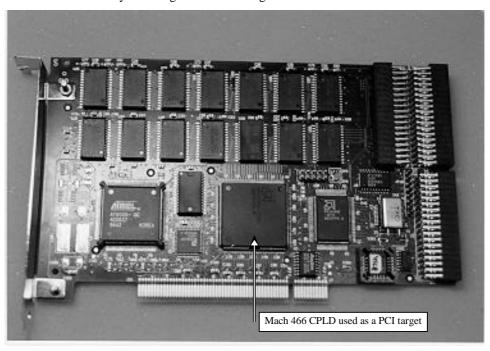

| FIGURE 54 - GM256, FOURFOLD'S CPLD BASED PCI DRAM CARD                                 | 84    |

|----------------------------------------------------------------------------------------|-------|

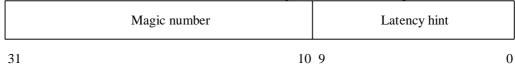

| FIGURE 55 - A POSSIBLE ARRANGEMENT OF A LATENCY HINT WORD                              | 85    |

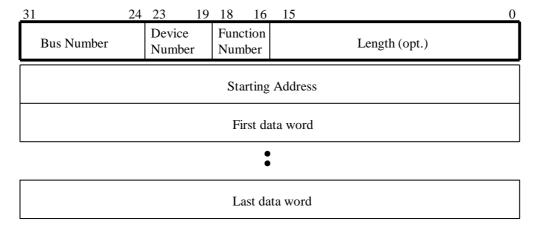

| FIGURE 56 - SPLIT TRANSACTION REQUEST - METHOD 1                                       | 86    |

| FIGURE 57 - SPLIT TRANSACTION REPLY - METHOD 1                                         | 87    |

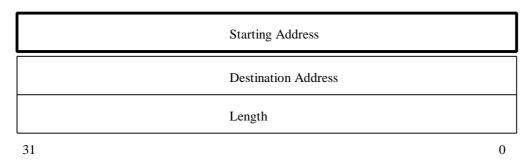

| FIGURE 58 - SPLIT TRANSACTION REQUEST - METHOD 2                                       | 87    |

| FIGURE 59 - SPLIT TRANSACTION REPLY - METHOD 2                                         |       |

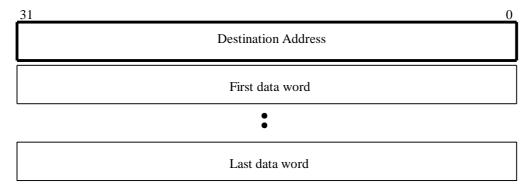

| FIGURE 60 - SPLIT TRANSACTION REQUEST - METHOD 3                                       | 88    |

| FIGURE 61 - SINGLE MASTER PERFORMANCE AS A FUNCTION OF THE INITIAL RETRY THRESHOLD AND |       |

| MASTER RETRY OVERHEAD                                                                  | . 102 |

| FIGURE 62 - MULTIPLE MASTER PERFORMANCE AS A FUNCTION OF THE ARBITER MTT AND THE TARG  | ΈT    |

| INITIAL RETRY THRESHOLD                                                                | . 103 |

| FIGURE 63 - MULTIPLE MASTER PERFORMANCE AS A FUNCTION OF THE ARBITER MTT AND THE MLT   | 104   |

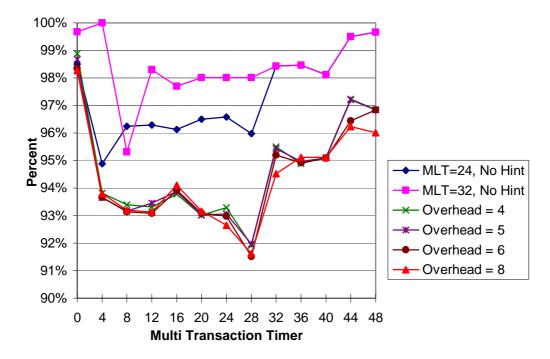

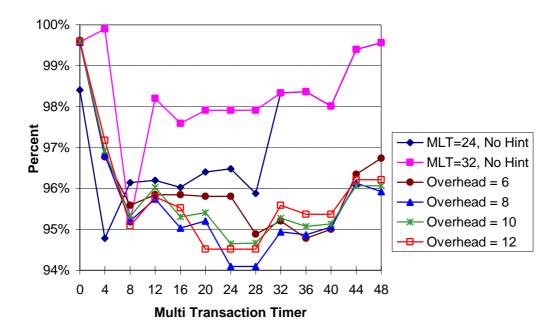

| FIGURE 64 - MULTIPLE MASTER PERFORMANCE WITH TARGET RETRY HINT, MLT=24                 | . 104 |

| FIGURE 65 - MULTIPLE MASTER PERFORMANCE WITH TARGET RETRY HINT, MLT=32                 | . 105 |

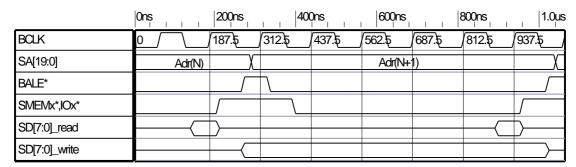

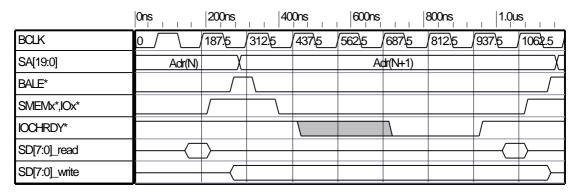

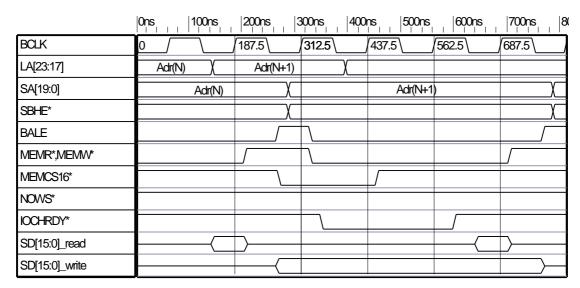

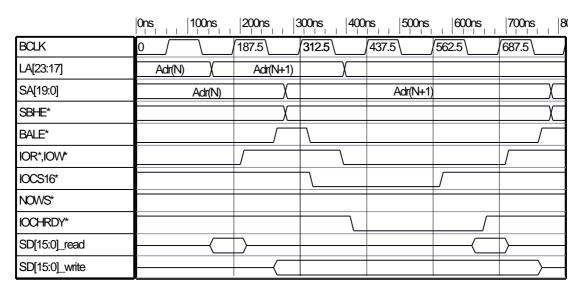

| FIGURE 66 - ISA 8 BIT STANDARD MEMORY AND I/O CYCLE                                    | . 112 |

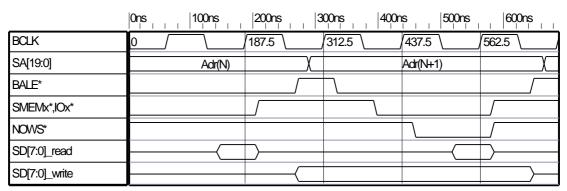

| FIGURE 67 - ISA 8 BIT NO WAIT STATES MEMORY AND I/O CYCLE                              | . 112 |

| FIGURE 68 - ISA 8 BIT, MEMORY AND I/O "READY CYCLE"                                    | . 113 |

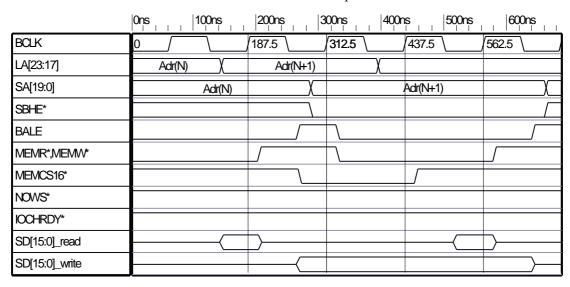

| FIGURE 69 - ISA 16 BIT STANDARD MEMORY CYCLE                                           | . 113 |

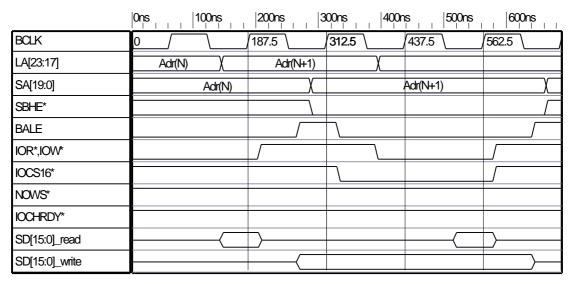

| FIGURE 70 - ISA 16 BIT STANDARD I/O CYCLE                                              | . 114 |

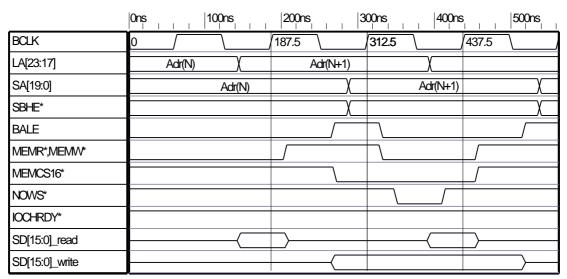

| FIGURE 71 - ISA 16 BIT NO WAIT STATES MEMORY CYCLE                                     | . 114 |

| FIGURE 72 - ISA 16 BIT MEMORY "READY CYCLE"                                            | . 115 |

| FIGURE 73 - ISA 16 BIT I/O "READY CYCLE"                                               | . 115 |

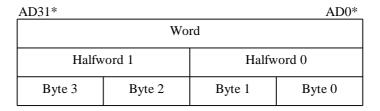

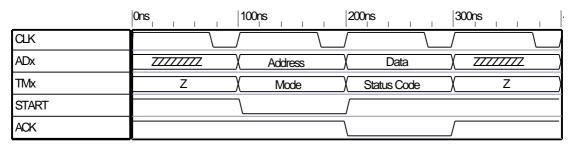

| FIGURE 74 - NUBUS DATA TYPES                                                           | . 117 |

| FIGURE 75 - NUBUS ZERO WAIT STATE READ AND WRITE CYCLES                                | . 118 |

| FIGURE 76 - NUBUS ONE WAIT STATE WRITE CYCLE                                           | . 119 |

| FIGURE 77 - NUBUS ONE WAIT STATE READ CYCLE                                            | . 119 |

| FIGURE 78 - NUBUS READ BURST CYCLE                                                     | . 119 |

| FIGURE 79 - NUBUS WRITE BURST CYCLE                                                    | . 120 |

| FIGURE 80 - NUBUS ARBITRATION LOGIC                                                    | . 121 |

## **List of Tables**

| Table 1 - Data and Address Bus                                                                     | 22  |

|----------------------------------------------------------------------------------------------------|-----|

| TABLE 2 - THROUGHPUT                                                                               | 22  |

| TABLE 3 - BUS CLOCK AND NUMBER OF SLOTS                                                            | 23  |

| TABLE 4 - LOCKING AND SNOOPING                                                                     | 24  |

| TABLE 5 - PLUG AND PLAY                                                                            | 25  |

| Table 6 - DMA and interrupts                                                                       | 25  |

| Table 7 - PCI related industrial standards                                                         | 27  |

| TABLE 8 - PCI BYTE ENABLE MAPPINGS                                                                 | 48  |

| Table 9 - PCI commands                                                                             | 48  |

| TABLE 10 - PCI ADDRESSING MODE FOR MEMORY READ/WRITE COMMANDS                                      | 53  |

| $TABLE\ 11\ -\ LEGAL\ CBE\#[3:0]\ \ AND\ AD[1:0]\ \ COMBINATIONS\ FOR\ I/O\ READ/WRITE\ COMMANDS\$ | 54  |

| TABLE 12 - PCI COMMAND CONFIGURATION REGISTER                                                      |     |

| TABLE 13 - PCI STATUS CONFIGURATION REGISTER                                                       | 57  |

| TABLE 14 - PCI BIST CONFIGURATION REGISTER                                                         | 58  |

| TABLE 15 - PCI BRIDGE IO_BASE DECODING                                                             | 65  |

| TABLE 16 - PCI BRIDGE CONTROL REGISTER                                                             | 66  |

| Table 17 - CPLD vs. FPGA features                                                                  | 70  |

| TABLE 18 - PCI TIMING PARAMETERS                                                                   | 73  |

| TABLE 19 - MACH465-12 PCI STATIC TIMING ANALYSIS PARAMETERS                                        | 74  |

| TABLE 20 - MACH465-12 TIMING CHARACTERISTIC PARAMETERS                                             | 74  |

| Table 21 - Proposed encoding for New Split transaction PCI commands                                | 86  |

| TABLE 22 - LOGIC STATE RESOLUTION TABLE                                                            | 92  |

| TABLE 23 - LATENCY HINT SIMULATION MASTER PARAMETERS                                               | 100 |

| TABLE 24 - LATENCY HINT SIMULATION TARGET PARAMETERS                                               |     |

| Table 25 - ISA wait states                                                                         | 111 |

| TABLE 26 - ISA CYCLE WIDTH ENCODING                                                                | 111 |

| TABLE 27 - NUBUS TRANSFER TYPE ENCODING                                                            | 118 |

| Table 28 - NuBUS status codes                                                                      | 118 |

| TABLE 29 - NUBUS BLOCK TRANSFER.                                                                   | 119 |

| TABLE 30 - NuBUS ATTENTION CYCLE CODES                                                             | 121 |

## 1. Introduction to the PCI Bus Architecture

The PCI (Peripheral Component Interconnect) local bus [(PCISIG, 1995), (Shanley, 1995), (Kendall, 1994)] is a high speed bus. The PCI Bus was proposed at an Intel Technical Forum in December 1991, and the first version of the specification was released in June 1992. The current specification of the PCI bus is revision 2.1, which was released on June 1, 1995. Revision 2.2, which is due to be published soon, would add support for Hot insertion and removal of cards, power management, and incorporate several other ECRs that have been accumulated since Revision 2.1.

Since its introduction, the PCI bus has gained wide support from all the computer industry. Almost all PC systems today contain PCI slots, as well as the Apple and IBM Power-PC based machines, and the Digital Alpha based machines. The PCI standard has become so popular it influenced the creation of more than one related standard based on leveraging PCI technology.

The PCI Bus is designed to overcome many of the limitations in previous buses. The major benefits of using PCI are:

#### High speed

The PCI bus can transfer data at a peak rate of 132MBytes/sec using the current 32 bit data path and a 33MHz clock speed. Future implementations featuring a 64 bit data path and 66MHz clock speed may transfer data as fast as 524MBytes/sec. Even at its basic mode, PCI delivers more than tenfold the performance levels offered by its predecessor in the PC world, the ISA bus.

#### • Expandability

The PCI bus can be expanded to a large number of slots using PCI to PCI bridges. The bridge units connect separate small PCI buses to form a single, unified, hierarchical bus. When traffic is local to each bus, more than one bus may be active concurrently. This allows load balancing, while still allowing any PCI Master on any bus to access any PCI Target on any other PCI bus.

#### Low Power

Motherboards can lower their power requirement by reducing the clock rate as low as 0Hz (DC). All PCI compliant cards are required to operate in all frequency ranges from 0Hz to 33MHz.

#### • Automatic Configuration

All PCI compliant cards are automatically configured. There is no need to set up jumpers to set the card's I/O address, IRQ number, or DMA channel number. The PCI BIOS software is responsible for probing all the PCI cards in a system, and assigning resources to every card, as required.

#### • Future expansion

The PCI specification can support future systems by incorporating features such as an optional 64 bit address space, and 66MHz bus speed. The specification defines enough reserved fields in all the bus definitions (configuration space registers, bus commands, addressing modes), that any unforeseen enhancement will not hinder compatibility with present systems.

#### Portability

By incorporating the (optional) OpenBoot standard, any device with OpenBoot Firmware can boot systems containing any microprocessor and O/S. Even without OpenBoot, it is common to see drivers for many video cards and SCSI controller for multiple CPU architectures and operating systems.

#### • Complex memory hierarchy support

The PCI Bus supports advanced features such as bus snooping to allow cache coherency to be kept even with multiple bus masters, and a locking mechanism to support semaphores.

#### • Interoperability with existing standards

The PCI Bus allows interoperability with existing ISA cards by supporting subtractive decoding of addresses (allowing addresses not decoded by PCI cards to be routed to an ISA backplane). The standard also supports the fixed legacy addresses for VGA cards and IDE controllers (required for system boot). Another feature supporting backward compatibility allows different devices to respond to different I/O byte addresses even if they share the same 32 bit word.

## 2. Computer busses

It is widely recognized that the computer system bus affects the system characteristics in several important ways:

- The bus bandwidth and transfer parameters place a limit on the system performance.

- The system bus is an interface that connects hardware components produced by different vendors and provides interoperability.

- The wide variety of configuration options supported by increasingly complex and sophisticated I/O devices make manual configuration a difficult and error-prone task. Support for software-based automatic configuration has become a necessity.

- When multiple processors share a bus with common resources, some form of support for multiprocessing is required to arbitrate the use of shared resources.

Even though memories are getting faster, CPUs get faster quicker. Although the memory burst speed can be increased by using interleaving, the initial latency cannot be reduced, and in fact becomes the dominant factor in bus usage. This is just one of a number of parameters, other than demand for raw bus bandwidth, that have changed in recent years and must be considered in modern system bus design.

We describe design principles and tradeoffs in modern microprocessor system buses (FutureBus+, VME64, PCI) as well as some of their predecessors (ISA, MicroChannel, EISA, and NuBus) to provide perspective and a basis for comparison. The section consists of two main parts: description of bus architectures, and comparison and design tradeoffs. We begin the next section with a brief historical perspective.

#### 2.1 Historical Perspective

It is interesting to review the way microprocessor system buses have evolved beginning with the ISA and up to new modern buses, such as PCI, FutureBus+, and VME64, and how various tradeoffs and compatibility issues were addressed in each design.

#### ISA Bus

The ISA Bus [(Messmer, 1995), (Shanley & Anderson, 1995), (Solari, 1992)] originated in the IBM PC, introduced in 1981. In it's first version, the ISA Bus was only 8 bit wide, with a 1Mbyte addressing range. When the IBM AT was introduced, another connector was added along the original XT Bus connector, adding 8 additional data lines, 4 additional address lines, and more interrupt/DMA lines. There was no organization defining the ISA bus, so when more AT compatible machines appeared on the market, the ISA Bus became a de-facto standard. Only in a later stage the IEEE defined the ISA bus as IEEE 996, but this was done as an afterthought. In fact, the objective of new systems having ISA slots is to be compatible with as many ISA cards as possible, IEEE compliant or not. Later on, Plug and Play was added to ISA bus. There are even a few non x86 based machines using the ISA bus (some SGI machines).

#### MicroChannel (MCA)

When IBM introduced it's PS/2 line of computers in 1987, one of the key features in IBM's attempt to recapture the PC market was the MicroChannel bus [(IBM, 1989), (Pescatore, 1989)]. This was a completely new bus that had improved characteristics such as automatic configuration (no hardwired addresses), faster speed, and optional 32 bit data and address support. The MicroChannel was incompatible with the ISA Bus, however. IBM's licensing agreement required manufacturers to pay IBM for every MicroChannel based machine they sold, a policy which, in retrospect, might have been a major reason for the MicroChannel's failure to gain a substantial market share. The MicroChannel was also used on some of IBM's RS6000 workstations.

#### **EISA**

Compaq decided to solve the same problem solved by IBM's MicroChannel bus, using a different approach. The EISA Bus [(Messmer, 1995), (Solari, 1992)] was designed to be backward compatible with the ISA Bus by using a unique connector which was compatible with the ISA edge connector, but had additional pins for its extended functionality on a second row of contact fingers on the PCB's edge connector. This allowed EISA based machines to use old ISA cards as well as the new EISA cards in the same slots. Old ISA cards would simply connect only to the top row of connectors on the EISA socket, while EISA cards has longer fingers reaching the lower row of connector fingers. EISA cards could not be used on ISA machines, even in ISA mode, due to the longer EISA edge connector. Like MicroChannel, EISA hasn't really caught on, since EISA cards were much more expensive. EISA was used mainly on server machines which required multiple network cards and multiple disk controllers, which made efficient use of the bus mastering features and the extra bandwidth of this bus.

#### **VME**

VME [(Peterson, 1989), (VITA, 1994)] is the standard bus type on high performance multiprocessor servers, and high end embedded systems. VME began it's life as a 16 data bit/24 address bit bus for 680X0 based machines called VERSAbus. VERSAbus was later modified to use the EuroCard form factor, and was renamed to VME (Versa Module Eurocard). Today VME supports 32 data bit/32 address bit cards, and VME64 supports 64 bit cards. VME system supports all popular microprocessors today, including the 680X0, the SPARC, the Alpha, and the X86.

#### NuBus

The NuBus [(Byte, 1987), (MR, 1987)] standard originated at MIT in 1979. Western Digital bought the rights to the NuBus technology from MIT in 1981, but later sold the rights to Texas Instruments, which used it for it's Explorer line of LISP machines and System 1500 Unix system. When Apple introduced the Mac II, it incorporated NuBus slots. NuBus is also an IEEE standard, IEEE 1196. It uses the same DIN connector as VME, but has a card form factor similar to that of a PC card. NuBus bears some similarity to PCI. Both buses are 32 bit, multiplexed, synchronous, and support an automatic configuration mechanism.

#### FutureBus+

The FutureBus+ [(Aichinger, 1992), (IEEE, 1990), (Theus, 1992)] standard has a long history. Work began on FutureBus in 1979 (prior to VMEbus). The specification produced was very similar to VME, but the sponsoring committee felt it wasn't "good enough" and sent the specifications back to the FutureBus committee. This led to the collapse of the working group, and only in 1984 the foundation for a new specification was laid. The specifications were prototyped in 1985 and the first FutureBus+ (notice the name change!) systems were shipped in Tektronix 32032 based workstation in 1986. In 1987, the standard was published as IEEE 896.1-1987. In 1989 FutureBus+ was independently selected as the baseline specification by the VME International Trade Association (VITA) for it's "Next Generation Architecture Bus Standard". It was also chosen for the Telecom industry's "Rugged Bus", and the Navy's "Next Generation Computer resources" (NGCR) program for mission-critical computing.

#### Local Buses: VESA and PCI

When 486 machines became widely available, it was necessary to have a standard for 32 bit cards that could provide fast video and disk performance. Since EISA was expensive, a much simpler design appeared on the market, the VESA (Video Electronics Standards Association) Local Bus [(Messmer, 1995)]. VESA Local Bus is mostly an extension of the 486 CPU bus, routed to an external connector. The VESA Local Bus was added as the third connector in the XT/AT ISA connector row, which means that all VESA Local Bus cards are long cards. The VESA Local Bus had a very limited goal (accelerating video and hard disks), so it's design is simple and cheap. The VESA Local Bus disappeared from the market when the Pentium and the PCI bus [(Shanley, 1995)] have arrived, for a few reasons:

- Local Bus cards are inherently more expensive than PCI cards, because they are longer (use more PCB material) and use a very long edge connector with golden fingers. They are also mechanically less reliable.

- The Local Bus specification is less advanced than PCI (limited burst capabilities, no plug and play, no bridges, limited number of slots).

- 486 based machines did not require an interface chip for the local bus, making local bus

motherboards cheaper than PCI motherboards. The introduction of the Pentium with its entirely

different system bus required a Local Bus interface chip, which made Pentium Local Bus

motherboards as expensive as PCI based motherboards.

#### LPC - Low pin count

LPC [(Intel, 1997)] is a very recent standard proposed by Intel (V1.0 is dated Sep 27, 1997) designed to replace ISA for motherboard peripherals (serial ports, parallel port, floppy interface, on-board audio). Instead of the hard-to-design ISA interface, which also has many lines (at least 36), a new interface with a minimum of 6 signals for a host, and 7 signals for a target was proposed. The interface was inspired by PCI and is synchronous (Usually slaved to the PCI clock rate), and has only a clock line, reset line, one control line (LFRAME#), and 4 bi-directional address/data pins. The new interface is slightly faster than ISA and supports all the legacy ISA functions (memory and I/O R/W, interrupt request, DMA request, bus masters), all at their legacy addresses. With the new LPC standard it is possible to design a Super-IO chip (The industry nickname for the chip containing the serial/parallel/floppy interfaces) with a reduced pin count (up to 88 pins, down from 160 pins), thereby reducing cost and board space. The same can be applied to an on-board SoundBlaster compatible audio interface, also using legacy ISA resources.

LPC contains a few improvements over ISA, including support for 4GB memory addressing (unlike ISA's 16MB), support for power down modes, and I/O & Memory cycle retries in an SMM handler.

LPC does **not** support the ISA Plug and Play mechanism, since LPC is intended for motherboard-only peripherals. These peripherals are known to the BIOS writer, and there is no need to probe the bus, looking for these devices.

LPC has no defined connector pinout, and there is **no** intention to produce LPC cards. The only expansion slot type in the next generation PCs would be PCI (and one AGP slot for a video card).

#### 2.2 Bus Architectures

#### **ISA**

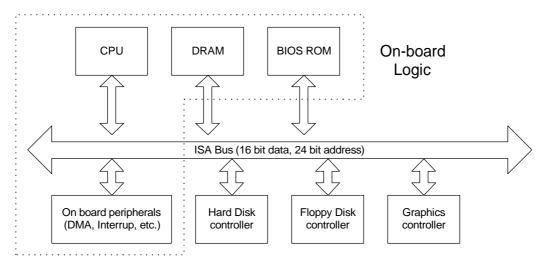

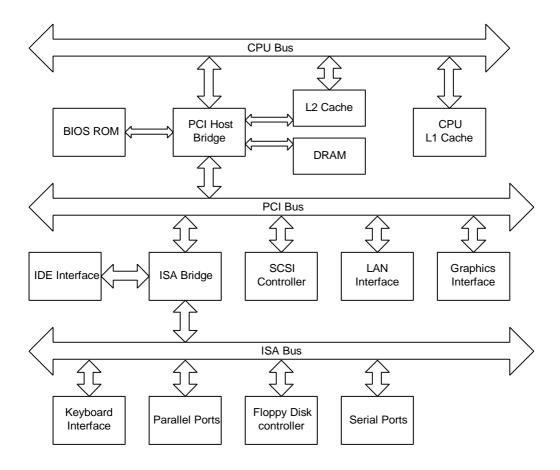

An ISA system consists of a single bus through which the CPU is connected to all the peripherals. In early PC systems, memory was also on the ISA bus, As shown in Figure 1. When CPU clock rates have broken the 8MHz barrier, the main CPU memory was moved to the local CPU bus to run at the CPU clock speed, instead of the ISA bus speed (8MHz), as shown in Figure 2. Some of the peripheral chips were integrated into the chipset, and are no longer directly on the ISA bus.

Figure 1 - Classic ISA system

Figure 2 - Modern ISA system

The bus signals are asynchronous, and are derived from the original 8088 and 80286 CPU bus. The bus is normally controlled by the CPU or DMA controller, which means that almost all ISA cards are simple slaves. The ISA bus also supports external bus masters, but almost no cards use this feature. The ISA bus does not support bursts and until recently did not support Plug and Play.

This structure is simple and requires very little logic to control and access the bus. On the other hand, at 8MHz the bus performance is not high, with a theoretical rate of 8MB/s for write, and 5.33MB/s for read.

Comparing the ISA bus to PCI, its only advantage is its simplicity. Simple cards can be built from cheap TTL components. The slow speed of the ISA Bus, and the low pin count of TTL devices makes it possible to build cards using Wire-Wrapping techniques.

The ISA has numerous drawbacks compared to PCI: Until recently, it had no Plug and Play standard, it can't share interrupt lines, it is only 16 bit wide, it is slow, and even then it is almost impossible to realize the full ISA bandwidth potential, due to limitations of the definition of the ready and wait state bus lines.

Since the ISA Bus is widely used, it is of special importance, and therefore we will discuss the ISA Bus structure in more detail in Appendix A.

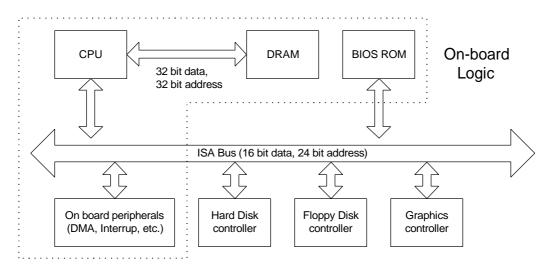

#### **MicroChannel**

The MicroChannel bus supports a 16-bit I/O address space, as in the AT, and a 24-bit (optional 32-bit) memory address space. Data ports participating in the transfer may be 8-, 16-, or 32-bit wide, and the port size may change dynamically, in every cycle. The MicroChannel supports single or burst transfers, and a bus arbitration method with 16 priority levels. A DMA controller provides DMA services to devices connected to the bus. Finally, a software-based configuration method eliminates the need for DIP switches and jumpers.

Figure 3 - MicroChannel architecture

Figure 3 illustrates a typical MicroChannel system. Transfers occur between a *master* and a *slave*. A master drives the address and control signals, such as timing strobes and the direction of the transfer. To perform a transfer, a master must become bus owner. To that end, a master must request the bus, and wait until it is granted the bus after one or more arbitration cycles. Then it can execute one or more transfer cycles, and relinquish the bus. The MicroChannel supports 16- and 32-bit masters. In addition to bus masters, there are two special masters: the system master and the DMA controller. The system master configures all MicroChannel adapters. Normally, the system master is the default master. It has the lowest arbitration priority, and it owns the bus when nobody else does.

The DMA controller transfers data between two slaves. The DMA controller is a master in the sense that it drives the address and control signals. The arbitration, however, is done by the slaves participating in the transfer.

A slave can participate in a transfer in either direction, under the control of a master. There are 8-, 16-, and 32-bit slaves. A DMA slave is a special kind of slave, which performs a transfer to another slave via the DMA controller. Like all slaves, a DMA slave does not drive address and control signals. Unlike other slaves, a DMA slave requests the bus, participates in arbitration cycles, and is granted the bus according to its own arbitration level.

The MicroChannel architecture defines a Central Arbitration Control Point (CACP), whose function is to initiate arbitration cycles when one or more requests are pending, and to allow sufficient time for resolution. Every adapter capable of requesting the bus is allocated a unique, four-bit arbitration level, at system start up. Arbitration levels range from 0000 to 1111 in descending priority order, with 1111 (lowest) assigned to the default master.

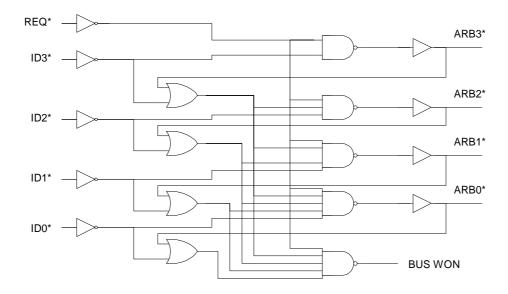

When the CACP begins an arbitration cycle, each requesting adapter drives its arbitration level on the four-bit arbitration bus. The resolution is decentralized and is performed by arbitration logic implemented in each adapter that can request the bus. An adapter that identifies a higher priority level on the arbitration bus must withdraw its request from the current arbitration cycle. The CACP allows sufficient time for this process, at the end of which the level of the device with the highest priority level remains on the arbitration bus. That device becomes the next bus owner. This logic is very similar to the NuBUS arbitration logic, which can be seen in Figure 80.

In burst mode, a device may remain the bus owner as long as no other devices request the bus. If there is another device requesting the bus, the bursting device must release the bus with the time limit specified by the MicroChannel specification. To prevent situations in which low priority devices wait indefinitely for the bus, likely to occur in systems that support high-priority bursting devices, the MicroChannel defines a fairness algorithm that work as follows. When an adapter is preempted, it cannot participate in another arbitration cycle as long as other devices are waiting for the bus. This guarantees that all pending requests are granted in their priority order, and no device will be granted the bus for the second time until all requesting devices have received access to the bus. Only bursting masters are required to implement the fairness algorithm. This algorithm is also used by NuBUS bus masters.

#### **EISA**

The EISA architecture is quite similar to the MicroChannel architecture shown in Figure 3. To remain compatible with ISA, EISA allows the use of ISA cards, and also retains the maximum 8.33 MHz clock rate. The EISA bus controller (EBC) supports 32- and 16-bit EISA adapters, and 16- and 8-bit ISA adapters. Transfers may occur between ports with different widths. For example, assume a 32-bit EISA bus master performs a write to an 8-bit ISA slave. The bus master gains access to the bus and drives address and data signals on the bus. The 8-bit ISA slave indicates it can only perform 8-bit transfers. At this point, the EISA bus controller takes over and drives on the bus the same signals as the bus master. Then the bus master deactivates its drives, and the signals, now driven only by the bus controller, remain steady on the bus. Finally, the bus controller splits the 32-bit data into four ISA byte writes. Read accesses are accumulated and combined into 32-bit reads in a similar way. The EBC implements the logic that splits/combines data and generates multiple access cycles, and bus masters are not required to duplicate it.

EISA supports burst cycles. There is also a more recent specification of an enhanced burst cycle, that provides higher transfer rates while keeping the bus clock at 8.33 MHz for compatibility. A 66Mbyte/s rate is achieved by performing 32-bit burst transfers on both edges of the clock. A 133Mbyte/s rate is achieved by multiplexing the 32-bit address bus to transfer 64 bits (using both the address and data buses), on both edges of the clock.

A common problem in ISA machines is the lack of interrupt lines. EISA solves this problem by allowing interrupt levels to be level-sensitive, instead of edge-triggered. Multiple devices may share the same interrupt line. While one device is serviced, the interrupt line remains active indicate pending interrupts from other devices. ISA adapters are edge-triggered, and require separate interrupt lines even if plugged into an EISA bus. Only multiple EISA adapters can share the same line.

#### **VME**

VME systems are usually based on a passive backplane with one or more CPU cards, and one or more I/O cards. VME backplanes may have as many as 21 I/O cards thanks to its asynchronous bus structure. VME cards come in 3 sizes: 3U, 6U, and 9U. 3U cards has a single 96 pin connector, and only 16 bits of data and 24 bits of address. 6U cards has two 96 pin connectors. The extra connector is used to add 8 extra address lines, 16 data lines, and 32 user pins. The user pins allows extra user cables to be connected to the card through the back of the backplane, allowing rapid switching of cards without removing the cables from the card first. The user pins are also used for routing additional private busses between cards in addition to the VME bus. Most standard cards today are 32 bit wide 6U cards. 9U cards are even bigger, and have a third user connector.

The actual bus width is dynamic, and set during the transaction. A cycle begins by driving the address, a 6-bit address modifier code specifying the address width (16/24/32) and operation type (r/w), and the address select line. The data bus width is set using the DS[1:0], LWORDA and A01 lines. A 32 bit capable card will also accept 8 and 16 bit cycles. An 8 or 16 bit wide card may choose to accept 32 bit transaction, but it will have to ignore the extra data. VME cannot resolve data bus width like the 680X0 bus can.

A master card may choose to do address pipelining by starting a new address cycle before the current data cycle is finished. This is possible thanks to the non-multiplexed bus. The arbitration logic is daisy chained, and has 4 levels.

VME also optionally supports hot insertion and removal of cards which is a must for fault tolerant systems.

Some recent additions to the standard includes the VXI standard (VME based measurement instruments on a card controlled by software), allowing complex CPU controlled test and measurement systems containing multiple instruments. VXI inspired the creation of its PCI equivalent, the PXI bus (see section 3.1.5).

#### NuBus

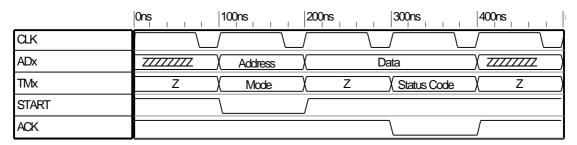

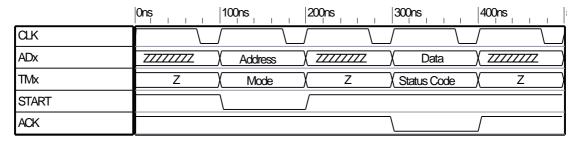

NuBUS is a 32 bit wide, 10Mhz synchronous bus. NuBUS uses standard VME type DIN connectors with 3 rows of 32 pins each. The clock signal is 75ns high, and 25ns low, with signals changing on the rising edge, and latching on the falling edge. This allows 25ns for hold time and clock skew. Every card has a unique slot ID which is used to map a unique 16MB memory area at the top 256MB of the memory map and is used for configuration. The bus itself is multiplexed with 32 bit for data and address. A simple, non-burst transfers involves driving the address and command lines for one cycle. The two lower bits of the command lines TM[1:0] and the two lower bits of the address lines AD[1:0] indicate the transfer size (byte/word/longword), alignment, and operation (read/write). The target acknowledges the cycle and returns status information (OK, error, timeout, or retry).

The theoretical non-burst data rate on NuBUS is 20MB/s by doing a 2 cycle read/write operation. In practice, read operations may take 3 cycles or more.

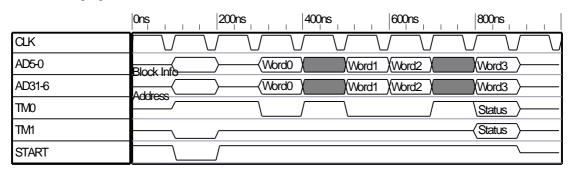

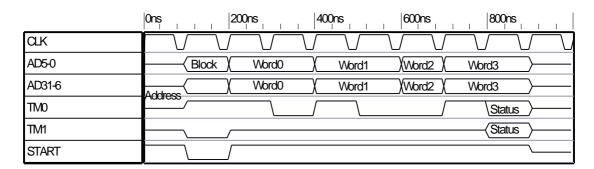

Block transfers are done in NuBUS by using two special TM[1:0] and AD[1:0] codes indicating burst read or burst write. Burst length is encoded using AD[5:2]. Possible burst lengths are 2, 4, 8, 16 longwords, and the starting address must be naturally aligned<sup>1</sup>. During burst, words are acknowledged by asserting TM[0], and ACK is generated only for the last word in the burst, with a status code. Since the longest burst is 16 longwords, the fastest possible cycle gives a peak transfer rate of 37.5MB/s. Non-burst capable boards can respond with ACK for the first word, which tells the bus master that bursts are not supported for this particular target.

Arbitration between bus masters is done via a 4-bit arbitration bus. A distributed algorithm similar to MicroChannel is used to select the winner. Bus fairness is guaranteed by not allowing the current bus master to arbitrate the next cycle while the current bus cycle is still running (other cards may do so). Bus locking may be achieved by keeping the card ID on the arbitration bus, with the request signal active, for multiple cycles.

<sup>&</sup>lt;sup>1</sup> A *naturally aligned* block must be 2<sup>N</sup> words long, and its start address must be an integer multiple of the block size. As a result, bits [N-1..0] of the block start address are always 0.

Interrupts are not supported by NuBUS. Instead, virtual interrupts can be generated by bus master cards which use the bus to write values to a predefined address. This address may be identified by the CPU support chips and be used to generate an interrupt on the local CPU bus.

Due to the close similarity between PCI and NuBUS, a complete technical description of NuBUS is found in Appendix B.

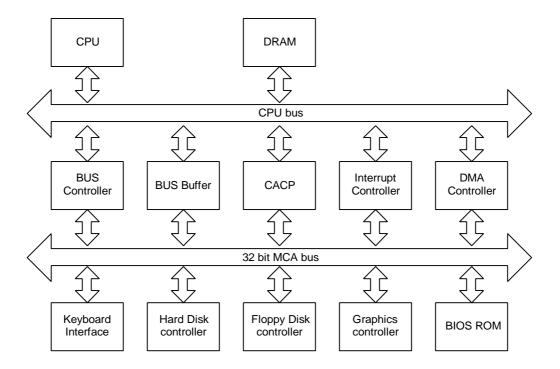

#### FutureBus+

The FutureBus+ standard is split into multiple sections:

- The electrical characteristics of the FutureBus+ signals such as signaling levels and load curves.

- The mechanical section defines the FutureBus+ form factor parameters such as card dimensions and the connector type used.

- The FutureBus+ protocol is the core of the standard, and defines the various signals and their behavior.

The use of separate definitions allows some parts of the standard to evolve, while staying compatible with other aspects of the bus.

Some of the special features of FutureBus+ can be summarized here:

- Architecture, Processor, and technology independence.

- No technology based upper limits. The only speed limiting factor in the standard should be

physical limitations (speed of light). The result of this guideline was an asynchronous bus which

can go faster as technology improves.

- Fault Tolerance: parity protection on all lines, fully distributed arbitration protocol (to reduce the risk of a single failure point), live insertion and removal of modules, dual bus operation, and fault detection and isolation mechanisms.

- Full support for cache coherency protocols, and split transactions.

- Message passing protocol for efficient multiprocessor communication.

- Full Support for bus to bus bridges. Bridges for the following buses has been defined in the standard: VMEbus, Multibus II and SCI (Scalable Coherent Interface) [(Tving, 1993)].

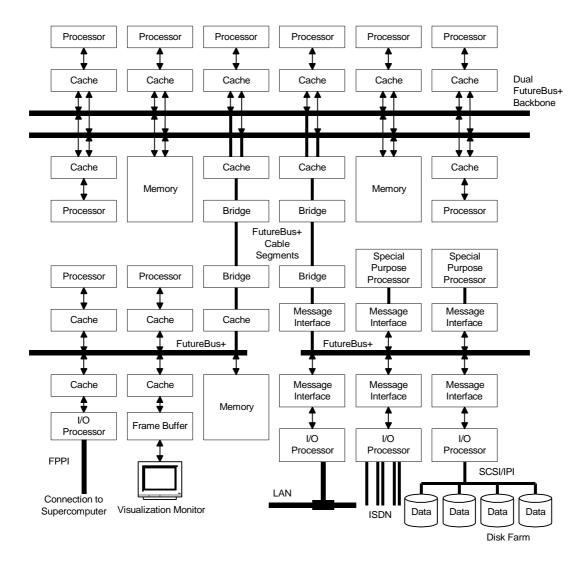

Figure 4 - FutureBus+ architecture

One of the major applications of FutureBus+ is multiprocessing, as illustrated in Figure 4. The most striking feature in Figure 4 is the hierarchy of buses interconnected by a set of bridges. The parallel protocol supports split transactions, required for efficient communications across buses. FutureBus+ integrates a MESI cache coherence protocol, and supports snarfing. While somewhat more complex to implement than a read invalidate protocol, snarfing allows cache-to-cache transfers of modified cache blocks without updating the memory. Snarfing can save significant bus bandwidth as it performs a single transfer of the modified cache block to the requester, rather than two transfers (memory write of the modified block followed by a memory read by the requester) in the simpler read invalidate protocol.

#### **PCI**

PCI is a *local* bus, sometimes also called an intermediate local bus, to distinguish it from the CPU bus. The concept of the local bus solves the downward compatibility problem in an elegant way. The system may incorporate an ISA, EISA, or MicroChannel bus, and adapters compatible with these buses. On the other hand, high-performance adapters, such as graphics or network cards, may plug directly into PCI (see Figure 5). PCI also provides a standard and stable interface for peripheral chips. By interfacing to the PCI, rather than to the CPU bus, peripheral chips remain useful as new microprocessors are introduced. The PCI bus itself is linked to the CPU bus through a PCI to Host bridge [(Wang et. Al., 1995)].

Figure 5 - PCI architecture

The basic PCI transfer is a burst. This means that all memory space and I/O space accesses occur in burst mode; a single transfer is considered a "burst" terminated after a single data phase. Addresses and data use the same 32-bit, multiplexed, address/data bus. The first clock is used to transfer the address and bus command code. The next clock begins one or more data transfers, during which either the master, or the target, may insert wait cycles.

PCI supports *posting*. A posted transaction completes on the originating bus before it completes on the target bus. For example, the CPU may write data at high speed into a buffer in a CPU-to-PCI bridge. In this case the CPU bus is the originating bus and PCI is the target bus. The bridge transfers data to the target (PCI bus) as long as the buffer is not empty, and asserts a not ready signal when the buffer becomes empty. In the other direction, a device may post data on the PCI bus, to be buffered in the bridge, and transferred from there to the CPU via the CPU bus. If the buffer becomes temporarily full, the bridge deasserts the target ready signal.

In a read transaction, a turnaround cycle is required to avoid contention when the master stops driving the address and the target begins driving the data on the multiplexed address/data bus. This is not necessary in a write transaction, when the master drives both the address and data lines. A turnaround cycle is required, however, for all signals that may be driven by more than one PCI unit. Also, an idle clock cycle is normally required between two transactions, but there are two kinds of back-to-back transactions in which this idle cycle may be eliminated. In both cases the first transaction must be a write, so that no turnaround cycle is needed, the master drives the data at the end of the first transaction, and the address at the beginning of the second transaction. The first kind of back-to-back occurs when the second transaction has the same target as the first one. Every PCI target device must support this kind of back-to-back transaction. The second kind of back-to-back occurs when the target of the second transaction is different than the target of the first one, and the second target has the Fast Back-to-Back Capable bit in the status register set to one, indicating that it supports this kind of back-to-back.

To reduce data transfer time on PCI, a bridge may combine, merge, or collapse data into a larger transaction. *Combining* refers to converting sequential memory writes into a single PCI burst transaction. For example, a write sequence of (32-bit) double words 1, 3, and 4 can be combined into a burst with four data phases, the second data phase having the byte enables off. Transactions whose order is not sequential, for example 4, 3, and 1, must remain as separate transactions. *Merging* refers to converting a sequence of memory writes (bytes or 16-bit words) into a single double word. Unlike combining, merging can occur in any order. For example, bytes 1, 0, and 3 can be merged into the same double word with byte enables 0, 1, and 3 asserted.

For arbitration, PCI provides a pair of request and grant signals for each PCI unit, and defines a central arbiter whose task is to receive and grant requests, but leaves to the designer the choice of a specific arbitration algorithm. PCI also supports *bus parking*, allowing a master to remain bus owner as long as no other device requests the bus. The default master becomes bus owner when the bus is idle. The arbiter can select any master to be the default owner.

Four interrupt lines are connected to each PCI slot. A multifunction unit may use all four, other units may use only a designated line (one of the four). The value in the Interrupt Line register determines which IRQ should be activated by the interrupt signal of the PCI unit. (For example, IRQ14 of the AT architecture, if the PCI unit is a disk adapter). The BIOS fills this field during system initialization. Later, when the operating system boots, the device driver reads this field to find out to which interrupt vector the driver's interrupt handler should be bound to.

PCI provides a set of configuration registers collectively referred to as "configuration space." By using configuration registers, software may install and configure devices without manual switches and without user intervention. Unlike the ISA architecture, devices are relocatable - not constrained to a specific PCI slot. Regardless of the PCI slot in which the device is located, software may bind a device to the interrupt required by the PC architecture. Each device must implement a set of three registers that uniquely identify the device: Vendor ID (allocated by the PCI SIG), Device ID (allocated by the vendor), and Revision ID. The Class Code register identifies a programming interface (SCSI controller interface, for example), or a register-level interface (ISA DMA controller, for example). As a final example, the Device Control field specifies whether the device responds to I/O space accesses, or memory space accesses, or both, and whether the device can act as a PCI bus master. At power-up, device independent software determines what devices are present, and how much address space each device requires. The boot software then relocates PCI devices in the address space using a set of base address registers.

## 2.3 Comparison and Design Tradeoffs

#### Address and Data Transfers

Usually the number of address pins (either separate address pins or multiplexed address/data pins) determines the amount of addressable memory on a bus. Some buses (and PCI specifically) can generate addresses larger than the bus width by splitting the address phase across two bus cycles. A card using a wider data bus can transfer data faster, but requires more pins, it is less reliable, requires more components, and is more expensive. Non only that, but any CPU with an N-bit wide data bus can hardly make effective use of a bus which is wider than N bits.

A multiplexed bus shares the same lines for both address and data. In a non-multiplexed bus, there are separate address and data lines. Non-multiplexed buses require more lines, but they are slightly faster on write (since address and data can be sent at the same time), and they can start a new read cycle (by driving the new address) while the current read cycle is still taking place. On the other hand, if a burst cycle is taking place, there are multiple data phases for every address phase, so the extra speed improvement by having a non multiplexed bus is relatively small. If the same lines used by a non multiplexed bus for addressing were used as extra data lines on a multiplexed bus, burst transfer would be faster on the multiplexed bus, using the same number of pins. Most new buses (PCI, FutureBus+, VME64) are multiplexed.

| Name                  | ISA     | EISA | MicroChannel | VME  | NuBus | FutureBus+ | PCI |

|-----------------------|---------|------|--------------|------|-------|------------|-----|

| Min. Data Bits        | 8 (XT)  | 32   | 16           | 16   | 32    | 32         | 32  |

| Max. Data Bits        | 16 (AT) | 32   | 32           | 64   | 32    | 256        | 64  |

| Min. Addr. Bits       | 20 (XT) | 32   | 24           | 24   | 32    | 32         | 32  |

| Max. Addr. Bits       | 24 (AT) | 32   | 32           | 64   | 32    | 64         | 64  |

| Multiplexed Addr/Data | No      | No   | No           | Both | Yes   | Yes        | Yes |

| Bus                   |         |      |              |      |       |            |     |

Table 1 - Data and Address Bus

In the first row of Table 1, the number of data bits refers to the minimum number of bits required on the implementation, not on the actual data transfer. For example, all EISA cards have 32 data bits, but not all data cycles are 32 bit. Some cycles may be 8 or 16 bit.

VME uses non-multiplexed 32 bit address/32 bit data bus. VME64 combines these address/data lines to a multiplexed 64 bit address/ 64 bit data bus. Note that Max. VME Addr./Data Bits (second and fourth row of Table 1) refer to VME64 only.

#### **Throughput**

Bus throughput calculations can be quite complex, so we mention only a few parameters here. The single word throughput measures the theoretical rate (in MB/s) at which an arbitrary single word read requests can be performed. The burst throughput is the theoretical rate at which reads can be performed (in MB/s) using the largest possible burst cycle possible on the bus.

When an address is transferred on the bus for every data word read or written, the bus is called non-bursting. When a bus can have a single address phase followed by multiple data phases (usually for consecutive addresses) the bus can do burst transfers. Burst data transfers lowers the overhead for large transfers (such as video screen manipulation and disk/networking I/O), by allowing the slave device to pipeline the subsequent data words while transferring the current word on the bus. It also removes the address phase overhead for every word.

| Name                  | ISA   | EISA      | MicroChannel | VME     | NuBus    | FutureBus+ | PCI        |

|-----------------------|-------|-----------|--------------|---------|----------|------------|------------|

| Max throughput,       | 8MB/s | 16.66MB/s | 13.11MB/s    | N/A     | 20MB/s   | 200MB/s    | 33.33MB/s  |

| Non Burst             |       |           |              |         |          |            |            |

| Max throughput, burst | N/A   | 33.33MB/s | 21.05MB/s    | 80 MB/s | 37.5MB/s | 4GB/s      | 133.33MB/s |

| Multiple Bus Masters  | Yes   | Yes       | Yes          | Yes     | Yes      | Yes        | Yes        |

| Split Transactions    | No    | No        | No           | No      | No       | Yes        | Some       |

Table 2 - Throughput

Referring to Table 2, the ISA throughput figure in the second row is based on no wait state cycles (2 clocks/cycle) at 8MHz with 16 bit data. This is a purely theoretical number, based on zero delay between the data request and the data acknowledge signals. The MicroChannel throughput figures are based on typical parameters. The maximum throughput, burst performance assumes a 190ns burst cycle time. A burst cycle in MicroChannel is the same as a non burst cycle, except for bus arbitration. Non burst cycles are allowed to use the bus only for one cycle. The VME data is for VME64. FutureBus+ specifies two transfer modes, an asynchronous (handshake) mode, and a synchronized packet mode. Packet mode is optional in FutureBus+ profile B. The max throughput non-burst data show in Table 2 are based on FutureBus+ profile B performance figures in for 64-bit asynchronous mode.

The ability to have multiple bus masters means that every card on the system can request the bus and generate read or write cycles by driving the address, data, and control pins. Cards on a bus with a single master cannot actively generate cycles on the bus. They can only be passively read or written.

Even though memories are getting faster, CPUs get faster quicker. Therefore if memory access time used to be less than 10 machine cycles, today the penalty for memory access may be a few dozen cycles. Although the memory burst speed can be increased by using interleaving, the initial latency cannot be reduced, and in fact becomes the dominant factor in bus usage. More time is spent on waiting for the initial latency, and less time is spent reading the data. By splitting the read request from the data transfer, the dead time between the request and the data transfer can be used to send more requests to other memory agents or to receive data from previous requests. This way the initial latency is not reduced, but the bus is free during that time for other requests and is not wasted.

Split transactions is a mechanism allowing a master to request data, disconnect from the bus, and have the target reconnect later to the bus and send the data when it is available. This allows other bus master to use the bus during the latency time.

PCI standard 2.1 requires a master accessing a target to retry the data transfer if it is encountering a target retry on the first data word. This allows a target with a very long latency to receive requests from masters, disconnect, and get the data to an on board buffer. When the master retries the same address, it will receive the data immediately. This is not a true split transaction, because the master can't really know when the target data is ready. If the master retries too early, it wastes bus bandwidth. If it retries too late, it will end up with a longer latency than what is needed, and limit the target's ability to queue additional requests, since buffer storage is wasted, waiting for the master to empty it.

#### Synchronous and Asynchronous Buses

In synchronous buses all the bus signals are sampled on the edge of a system clock. All signals obey the setup and hold requirements relative to the clock signals. This has the advantage that no handshaking is needed to transfer a single word. Asynchronous buses, on the other hand, are handshaking data transfer without any central clock signal. Control signals can change anytime without any restrictions.

Each bus has its limitations. An asynchronous bus can adapt well to different number of peripherals on the bus by giving better performance on a bus with a smaller load. A CMOS based asynchronous bus can drive a large number of slots or a very long bus (SCSI-1 is a good example of a potentially long asynchronous bus) without any problems, even at the price of reduced performance. A synchronous bus on the other hand will work faster, but will not work at all if the bus is overloaded or made longer, causing the total propagation delay to exceed the clock cycle time. If a synchronous bus is designed in advance to support a large number of slots or a long backplane, then the performance will be much worse, even when the same bus is not loaded with extra slots, because the clock rate is fixed

In section 4.2 we discuss synchronous and asynchronous busses in greater depth.

| Name                | ISA    | EISA    | MicroChannel | VME    | NuBus | FutureBus+ | PCI       |

|---------------------|--------|---------|--------------|--------|-------|------------|-----------|

| Bus Clock           | 8MHz   | 8.33MHz | Async.       | Async. | 10MHz | Async.     | 0 - 33MHz |

| Number of Bus slots | Undef. | 15      | 15           | 21     | 15    | 32         | 4         |

Table 3 - Bus clock and number of slots

The number of bus slots determines the expandability of the bus. Usually a bus has both architectural limitations to the number of slots, as well as electrical limitations. An example of an architectural limitation is the number of bits of a slot ID code, while an electrical limit is, for example, the 10 load maximum for a pin in the PCI standard. An electrical limit can be overcome by improving technology without hurting compatibility while an architectural limit requires changes in the standard in order to be solved.

As we just said, the PCI standard allows 10 electrical loads per bus. A PCI peripheral on a card counts as two loads, while an on-board peripheral counts as one load. A motherboard can have, therefore, up to 4 slots (see Table 3). Since PCI buses can be linked with bridges (up to 256 buses), A theoretical maximum of 2560 on-board PCI devices can share one PCI system, (or up to 2050, excluding the bridges).

The number of ISA slots is not limited by the standard, but limited by practical implementations. Typical systems use up to 8 slots. Logically, it is possible to have 15 bus slots on EISA, MicroChannel, and NuBUS. EISA is limited by the pre-assigned configuration space at XC80h through XC84h. MicroChannel and NuBUS are limited by the 4 bit distributed arbitration logic. In practice, the EISA timing specifications are limiting the number of physical slots to 7. MicroChannel and NuBUS might have the same practical limitations.

#### Multiprocessing Support: Locking and Snooping

When multiple processors are sharing a common bus with common resources, a semaphore is required to arbitrate a specific resource between multiple processors. A semaphore is set by the processor requesting the resource, and cleared when the resource is freed. A semaphore must be read before it is set, because it might be already set. The semaphore read and set operations must be atomic because if two processor may read the semaphore at the same time and both see the semaphore is clear, they may both try to set it simultaneously.

Bus locking allows a specific memory range to be locked by a master, causing this memory area to be accessible only by the same master until the lock is released. A more limited way of bus locking is the Read-Modify-Write cycle which allows a master to read a word, modify it, and then write the result back to the same address, with a guarantee that no other master can access the bus between the read and the write operation. These hardware primitives allows the system software to build more complex locking mechanisms for resource arbitration between multiple processors.

In multiprocessor systems we usually find one or more processors with local cache memory on a common bus, sharing common memory which is also on the bus. A data coherency problem is caused by the local caches since data modified by one processor in memory is not reflected in another processor if that processor has a copy of that word on his local cache. Not only that, but on a write-back cache system a word may be written back to memory but in fact be written only to the write back cache. Later, a different word in the same cache line is written by a different processor, and flushed to memory. If the first word with its entire cache line is also flushed to memory, it will erase the rest of the cache line in memory, destroying newer data. A possible solution is bus snooping, which allows a processor to watch the bus all the time, invalidate (or update) its local cache copy of data which appears on the bus, and even allows it to interrupt a write cycle on the bus in order to flush its own write back cache first, before allowing the cycle to restart.

| Name         | ISA | EISA | MicroChannel | VME | NuBus | FutureBus+ | PCI |

|--------------|-----|------|--------------|-----|-------|------------|-----|

| Bus Snooping | No  | No   | No           | No  | No    | Yes        | Yes |

| Bus Locking  | No  | Yes  | No           | Yes | Yes   | Yes        | Yes |

Table 4 - Locking and snooping

Bus Locking is defined for PCI, but most targets don't support it. PCI bridge support is optional (since 2.1), and its usage is highly discouraged. Bus Locking is implemented in VME by a Read-Modify-Write cycle, unlike the PCI locking mechanism, which allows other transfers to take place while the lock is still in place.

Bus Snooping is essential for PCI, because modern PCI based systems typically have bus master PCI cards and local CPU caches with write back capabilities. The snooping mechanism is required when a dirty cache line is partially overwritten by an external PCI bus master.

#### Plug and Play

A Plug and Play capability is the definition of a standard way for a bus master to interrogate all the devices on the bus and identify them (including type, manufacturer, and model), their resource requirements (memory and I/O address space, interrupts, and DMA channels), assign specific resources to each device, or disable any specific device. It also defines a common header for an optional bootstrap ROM, which can do further device specific initialization. It can even go as far as defining a neutral language for ROMs which is processor independent, allowing the same card to run its initialization code on all processor types if their system software supports an interpreter for that language.

| Name            | ISA    | EISA | MicroChannel | VME | NuBus | FutureBus+ | PCI |

|-----------------|--------|------|--------------|-----|-------|------------|-----|

| "Plug and Play" | Yes/No | Yes  | Yes          | Yes | Yes   | Yes        | Yes |

Table 5 - Plug and Play

ISA "Plug N' Play" (or PNP) is a new standard, supported by some ISA cards only since 1995. A fully compliant ISA "Plug and Play" system requires a PNP aware motherboard, PNP cards, and a PNP aware operating system, such as Windows 95.

A VME board may contain CR/CSR registers which carry identification information and configuration registers, but since these are defined as optional, not all boards may have them.

All PCI cards are plug and play, but most PCI cards do not support the OpenBoot standard for neutral language boot code (only some Apple Macintosh PCI cards do). Some Power-PC system manufacturers have gone the trouble of implementing a software X86 emulator to allow booting from SCSI bus masters on Power PC based PCI systems.

#### Interrupt Support and DMA

There are many ways to implement interrupt support. Some buses have minimal interrupt support with no interrupt lines. A device can generate an interrupt by writing to a special address on the bus, or generating some other special type of bus cycle. Interrupt priority is handled by the regular bus arbitration logic. Most buses, however, have dedicated interrupt lines, which determines the maximum number of interrupt levels on the system. On systems which use level triggered interrupts, the interrupt event is active as long as the interrupt line is asserted, while edge triggered interrupts are generated during the transition of the interrupt lines from a low state to a high state or vice versa. Interrupt sharing is harder when using edge triggered interrupts, because edge transitions on an interrupt line which is already active are invisible.

DMA channels are a special feature that makes it easier to build a bus master card. Every DMA channel has a pair of handshake lines on the bus, which are connected to the DMA controller. A DMA transfer takes place after a program initializes the DMA channel by setting the data direction, base address, and number of words. The card will then read or write to the block of memory specified in the DMA channel registers simply by handshaking word transfers using the dedicated lines. The DMA controller takes care of the actual bus cycle generation, address generation, address increment, and word count. Since every DMA channel requires at least two lines per channel, and requires dedicated DMA logic, only a limited number of DMA channels are available.

| Name                 | ISA  | EISA       | MicroChannel | VME   | NuBus   | FutureBus+ | PCI   |

|----------------------|------|------------|--------------|-------|---------|------------|-------|

| Number of Interrupts | 6/12 | 12         | 11           | 7     | N/A     | N/A        | 4     |

| Interrupt type       | Edge | Level/Edge | Level        | Level | Virtual | N/A        | Level |

| DMA Channels         | 3/7  | 7          | N/A          | N/A   | N/A     | N/A        | N/A   |

Table 6 - DMA and interrupts

The 6/12 ISA interrupt lines and 3/7 DMA channels in Table 6 correspond to XT/AT cards respectively. EISA supports level-sensitive interrupts, but ISA adapters are edged-triggered, for compatibility reasons, even if plugged into an EISA bus. PCI defines 4 interrupt lines *per slot*, but these 4 lines aren't necessarily common to all slots. In theory a 4-slot PCI system may have 4 unique lines for every slot, and use as little as one or as many as 16 CPU interrupt lines.

Virtual Interrupts are predefined addresses in the memory map. A card that wishes to interrupt the CPU must act as a bus master and write to this address. Apple's version of NuBUS added a line called NMRQ (Non Master ReQuest), which acts like the usual interrupt line.

Physically, the MicroChannel bus does not define any DMA request/grant signals, but unlike other buses with no DMA signals, the MicroChannel system architecture specifies an on board DMA controller, which works by generating normal bus cycles, reading from the source and writing to the destination. This DMA controller does not require special bus support from the bus itself other than normal read/write cycles.

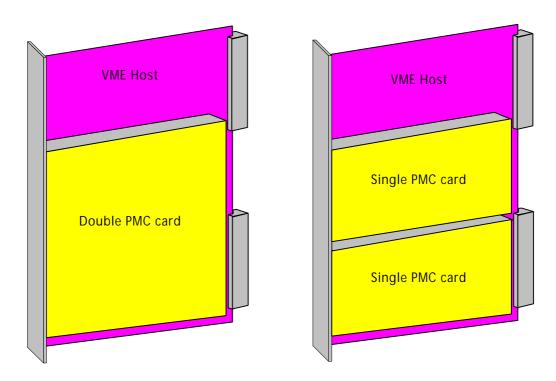

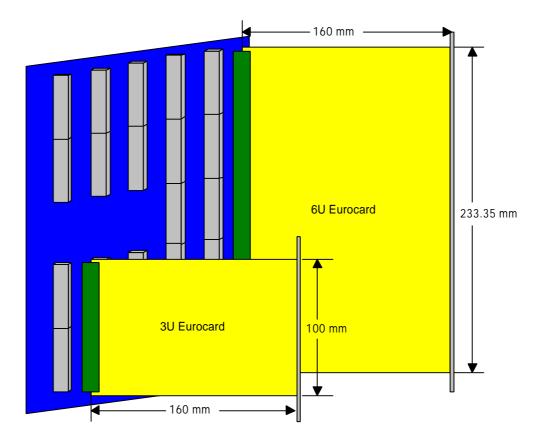

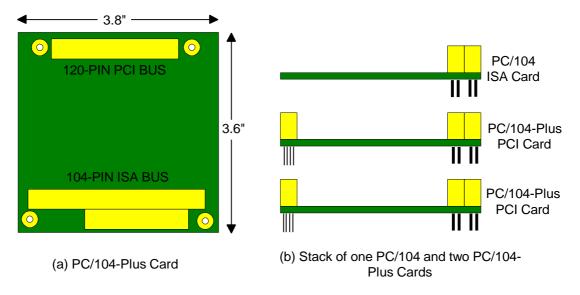

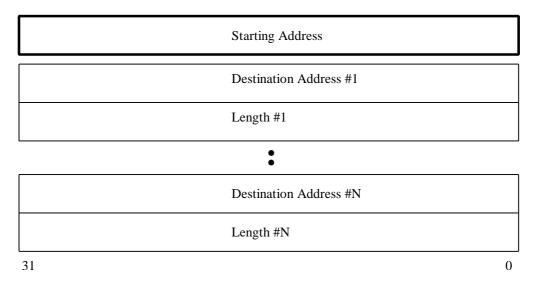

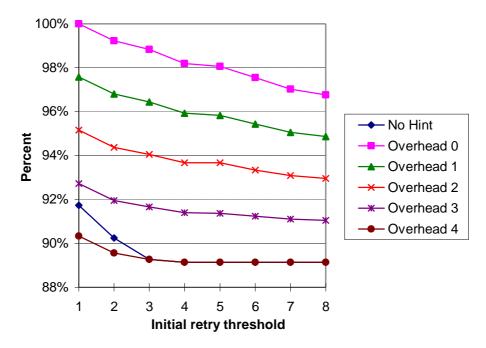

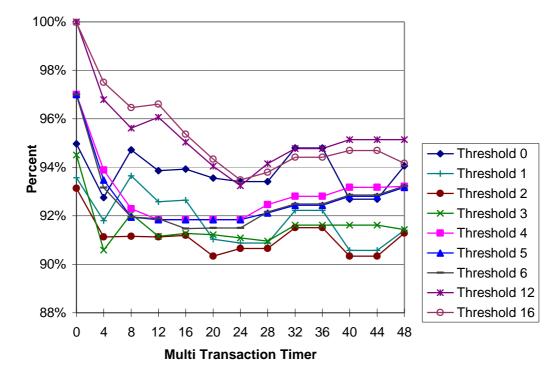

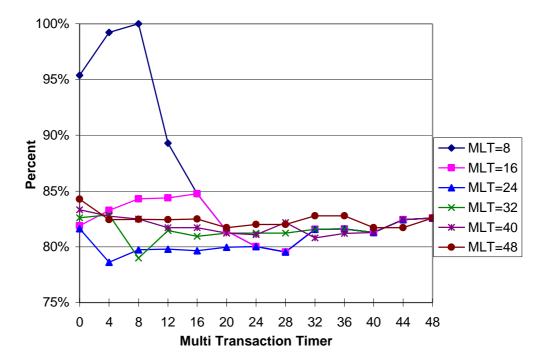

#### 3. PCI Bus related standards